I am designing a MIPS-like CPU with Verilog and now I'm handling data hazards. I have these instructions:

Ins[0] = LW r1 r0(100)

Ins[1] = LW r2 r0(101)

Ins[2] = ADD r3 r2 r1

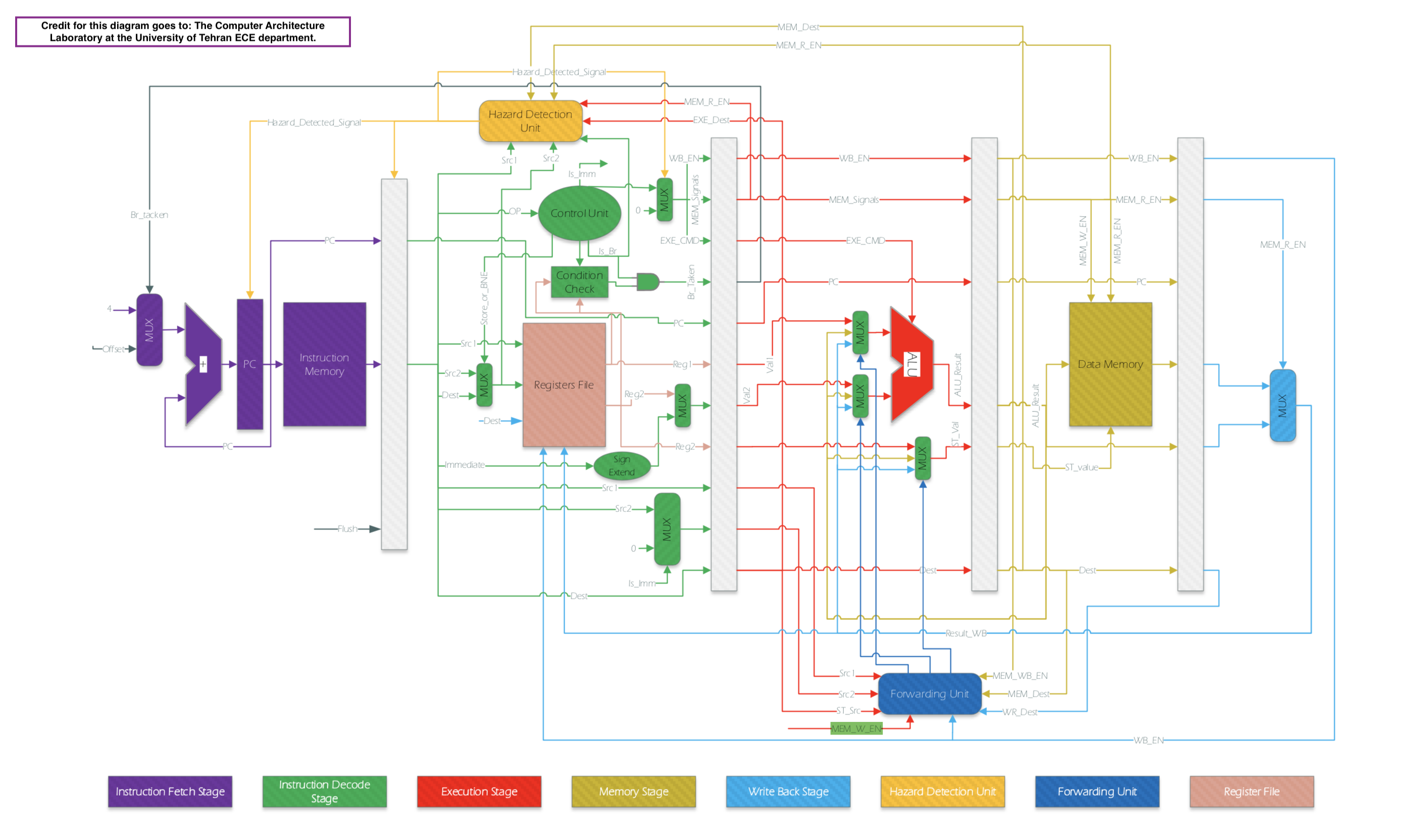

I'm using pipeline and my dataPath is something like this:

I have 5 stages, with 4 latch buffers separating them.

I have 5 stages, with 4 latch buffers separating them.

The problem is that when ADD instruction reaches stage3 (where the ALU should calculate r1 + r2), instruction 1 (the second LW) is in stage 4 and hasn't yet read the r0 + 101 address of the memory, so I should stall one cycle and after that Ins1 reaches the last stage.

In this situation, the first LW has finished its work and the new value of r1 isn't anywhere in dataPath but I need to pass this value to Input B of ALU.

(This is called data forwarding because when the third instruction was in stage 2 the value of r1 wasn't ready and I should forward it from later stages (The blue wires which come out from last MUX and go to ALU MUXs), but because of stall of second LW, I don't have the value of r1 furthermore.

Thanks for any help.

I made a mistake. My mistake is that when an LDM instruction is followed by RType I stall the processor when the Rtype is in stage3 and LDM is in stage4. but instead, I should detect the dependency one clock before that, when RType is in stage2 (decode) and LDM is in stage3 (exec).

In this situation, I should stall the pipeline.

So as the result when Rtype is in stage2, second LDM is in stage 3 and first LDM is in stage4, I detect the dependency and stall pipeline one cycle.

So in next clock, Rtype is still in stage2, second LDM in stage4 and first LDM is writing back to register and thus because the RType is still in stage2, it can read the data written to the register file. (Write back completes in negedge of the clock. In posedge, first argument of RType is ready.)